La industria de los semiconductores está atravesando una transformación radical. En un mundo donde más grande suele significar mejor —más núcleos, más GHz, más FLOPs— hay una métrica que desafía esa lógica: el tamaño del nodo de proceso. Cuanto más pequeño, mejor. Esta carrera hacia la miniaturización extrema no solo responde a la demanda de smartphones o computadoras, sino que está impulsada por la explosión de la inteligencia artificial (IA), que exige chips más densos, eficientes y potentes.

¿Qué es el nodo de proceso y por qué importa?

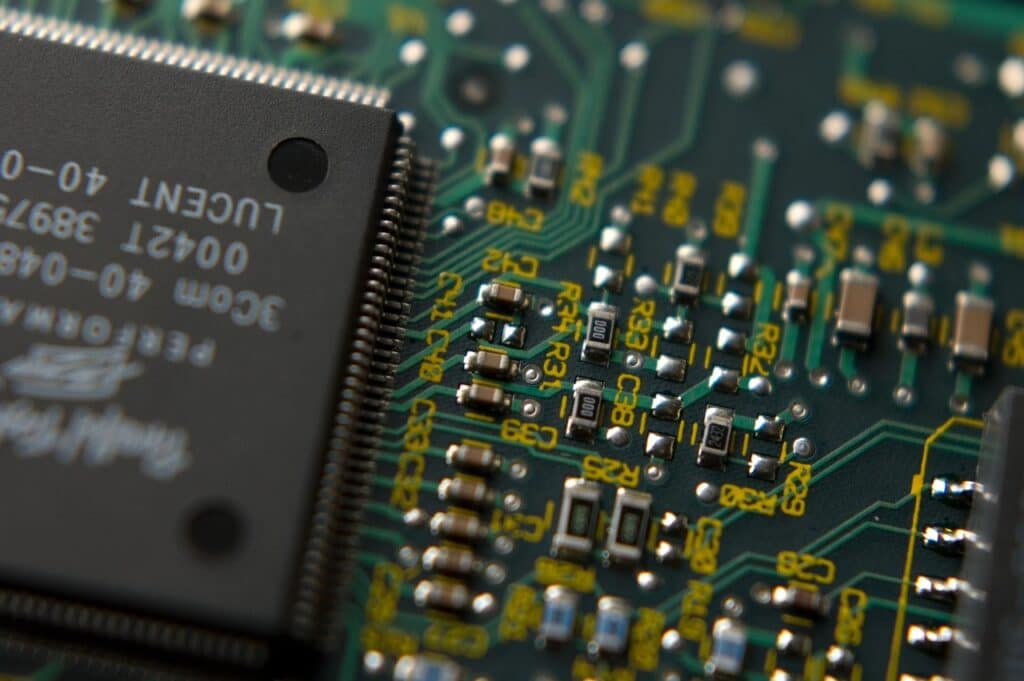

El nodo de proceso, medido en nanómetros (nm), representa el tamaño de las características más pequeñas que pueden fabricarse en un chip. Aunque hoy en día esta cifra se ha convertido en un término más comercial que técnico —ya que no siempre refleja la geometría real— sigue siendo un indicador clave de la densidad, eficiencia y rendimiento de los transistores.

Por ejemplo, un chip fabricado en 65 nm puede albergar cientos de millones de transistores, mientras que uno de 350 nm apenas llega a unos pocos millones. Esta diferencia no solo afecta el tamaño físico del chip, sino también su consumo energético y capacidad de cálculo. A menor tamaño, mayor velocidad de conmutación, menor disipación térmica y más operaciones por segundo.

La fotolitografía: el arte de imprimir átomos

La reducción del nodo de proceso se logra mediante una técnica llamada fotolitografía, que utiliza luz para grabar patrones microscópicos sobre una oblea de silicio. Sin embargo, la luz visible no es suficiente: sus longitudes de onda son demasiado grandes. Por eso, los fabricantes recurren a la luz ultravioleta extrema (EUV), con longitudes de onda de apenas 13.5 nm.

Esta tecnología permite crear estructuras de apenas unos pocos átomos de ancho. Pero no está exenta de desafíos: la precisión requerida es tan extrema que cualquier impureza, defecto o variación estadística puede comprometer la calidad del chip. Además, la energía de la EUV puede dañar los materiales si no se controla adecuadamente.

De FinFET a Gate-All-Around: reinventando el transistor

A medida que los nodos se acercan al límite físico del silicio, los fabricantes han tenido que rediseñar el transistor. La arquitectura FinFET, dominante en los últimos años, está siendo reemplazada por estructuras Gate-All-Around (GAA), como el RibbonFET de Intel. Estas nuevas configuraciones permiten un mejor control de la corriente y reducen las fugas eléctricas, esenciales cuando se trabaja a escala atómica.

El coste de fabricar lo imposible

La miniaturización no solo es un reto técnico, sino también económico. Fabricar chips en nodos de 3 nm o menos puede costar más de 20.000 dólares por oblea, y diseñar un nuevo chip puede superar los 500 millones de dólares. Para mitigar estos costes, los fabricantes han adoptado arquitecturas de chiplets: múltiples chips más pequeños combinados en un solo paquete. Esta estrategia mejora el rendimiento, reduce los defectos y permite una mayor flexibilidad en el diseño.

La demanda de chips avanzados proviene principalmente de los gigantes tecnológicos que desarrollan centros de datos para IA. Empresas como Microsoft, Google, Meta y Amazon están invirtiendo más de 250.000 millones de dólares al año en infraestructura de IA, lo que ha convertido la fabricación de chips en un activo estratégico global.

Pero la IA no solo impulsa la demanda: también está ayudando a optimizar la producción. Algoritmos de aprendizaje automático se utilizan para mejorar la fotolitografía, detectar defectos y aumentar el rendimiento de las obleas. En otras palabras, la IA está enseñando a las fábricas a sobrevivir a la presión que ella misma genera.

El futuro es vertical y apilado

A medida que nos acercamos al límite físico de la miniaturización, los avances ya no vendrán solo de reducir el tamaño, sino de ir en vertical. La integración 3D y el apilamiento de transistores permitirán crear chips más densos y eficientes, capaces de alimentar dispositivos portátiles, robots autónomos y centros de datos sin sobrecalentar la red eléctrica.

Intel, TSMC y Samsung ya están produciendo chips en nodos de 3 nm, y los de 2 nm están en fase piloto. El ritmo de innovación sugiere que cada 4.5 años se reduce el nodo a la mitad, lo que nos acerca a una era donde los chips serán literalmente estructuras de átomos organizados con precisión milimétrica.

La carrera por alcanzar el átomo no es solo una hazaña de ingeniería, sino una revolución que redefine los límites de la computación. Desde la arquitectura de los transistores hasta la economía global, cada aspecto de la fabricación de chips está siendo transformado por la necesidad de hacer más con menos. Y en el centro de todo está la inteligencia artificial, que no solo exige más potencia, sino que también ofrece las herramientas para lograrla.